Think skipping PCIe signal testing doesn’t matter? That only shifts the risk to the market and your customers.

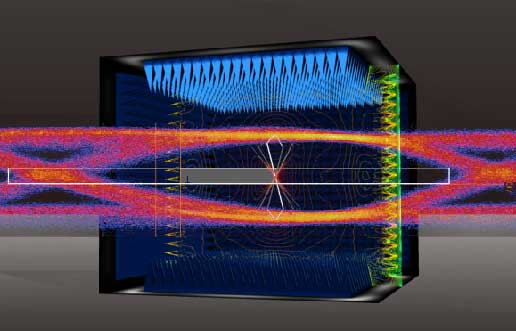

AI servers have fully entered the PCIe 6.0 era, with data volumes, bandwidth requirements, and computational loads all significantly increased. Today, end customers—whether CSPs, brands, or system integrators—care about more than raw performance. They want to ensure that in high-bandwidth, high-density architectures:

- Each PCIe signal lane is truly stable

- Every lane has been fully validated

- All channels remain error-free under PCIe 6.0’s high-speed environment

The devil is in the details. In fact, many system instabilities, GPU initialization failures, interrupted computations, throttled performance, delayed deliveries, and RMA issues often originate from high-speed lanes that were not fully tested.

Under PCIe 6.0 high-speed conditions, even a single unchecked lane can lead to serious risks:

- GPU fails to initialize or experiences frequent throttling

- AI model training is unexpectedly interrupted

- Computational performance falls short or produces unstable results

- Project deliveries are delayed

- RMA, returns, and brand trust are negatively impacted

Without full-lane (Full Lane) and full-preset (Full Preset) comprehensive validation, system stability is effectively left to “chance.”

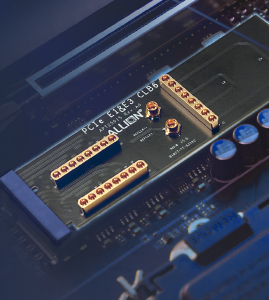

Golden Methodology × AEMS: Making Every PCIe Signal Visible

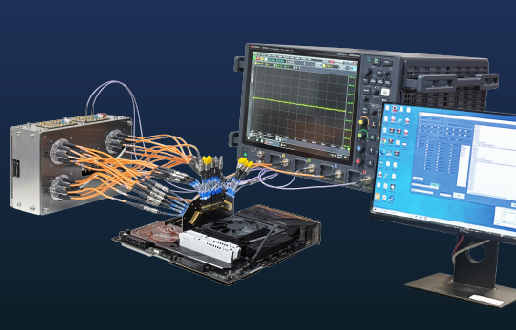

Allion has long participated in the PCI-SIG standards organization and contributed to building high-speed interconnect testing frameworks. By combining PCI-SIG–approved standard inspection procedures with Allion’s hardware and software development expertise, we have created the reliable and effective automated Golden Methodology. This full validation process is implemented in:

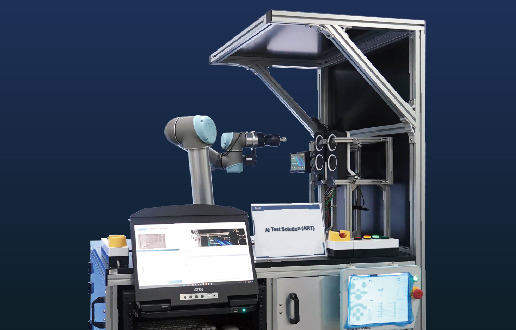

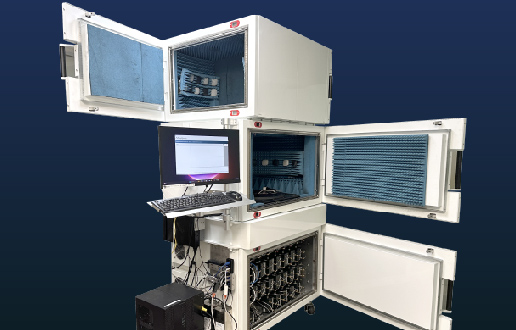

AEMS(Allion Electrical Multiport System)AEMS leverages high-precision, automated, multi-channel testing to overcome the limitations of manual measurements, giving buyers complete control over PCIe 6.0 signal quality—no longer relying on “sampling luck” or “engineer intuition.”

Traditional Testing vs AEMS

| Traditional Testing Key Pain Points for Buyers |

AEMS How It Addresses the Pain Points |

| Scenario → Limited test coverage; some lanes are never tested Risk → Increased performance and RMA risk |

Advantage → 100% full coverage Feature → Every channel is fully tested, leaving no blind spots and eliminating hidden signal risks |

| Scenario → Reliance on manual testing Risk → Inconsistent results; buyers cannot verify quality |

Advantage → Fully automated, standardized process × Golden Methodology Feature → Ensures every test result is stable, reproducible, and reliable |

| Scenario → Slow testing increases project delays Risk → Delivery schedules and customer commitments under pressure |

Advantage → Over 4× efficiency improvement; supports continuous overnight automated testing Feature → Compared to traditional methods that require extensive manual labor, AEMS dramatically increases testing efficiency and supports automated scheduling, significantly shortening project timelines |

| Scenario → To speed up testing, additional manpower and expensive instruments are required Risk → ODM passes extra costs to buyers, increasing expenses |

Advantage → Single-platform automated scheduling × auto lane switching Feature → Reduces the need for at least four engineers and eliminates additional instrument investments |

AEMS: A Fully Automated PCIe Signal Validation Platform for Comprehensive Quality Assurance

l Auto Lane Switch Control

Automatically switches lanes without manual intervention or configuration changes.

l Auto Measurement Sequencing

Performs measurements automatically according to PCI-SIG validation methods, ensuring every data point is accurate, reproducible, and traceable.

l Auto Report & Analytics

Generates complete, real-time analysis reports, enabling buyers to quickly assess whether signal quality meets requirements.

These features not only improve testing speed but also give buyers full visibility and control over PCIe signal quality.

Supporting PCIe 6.0 and All Major Form Factors with Zero Coverage Gaps

AEMS supports all mainstream Form Factors!

Enables full-coverage testing from the design stage:

- CEM

- OCP NIC 3.0

- EDSFF E1/E3

- U.2 / U.3

- M.2

This ensures consistent signal quality across design → validation → mass production phases of AI servers.

AEMS: Leading the PCIe 6.0 Validation Era, Giving Buyers Control Over Quality and Delivery

In the AI computing race, PCIe signals are no longer just a specification—they are a critical factor for customer confidence, including:

- On-time delivery

- Stable compute performance

- Reduced RMA

- Reliable brand reputation

With the Golden Methodology at its core, AEMS transforms PCIe 6.0 signal testing into a buyer-controlled, transparent, and comprehensive quality assurance process, achieving all the key factors for building brand trust.

AEMS ensures every PCIe signal is validated and every unit of compute performance is consistently stable.

Want to learn how to achieve full-lane, full-preset, zero-gap validation for your PCIe 6.0 platform? Contact Allion to establish truly reliable AI server quality standards.