Actual case description

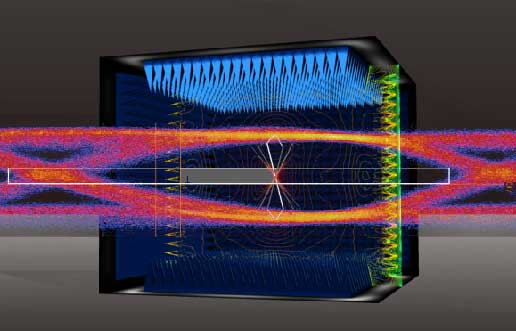

The client, a high-performance platform developer, was conducting DDR4 electrical validation for its next-generation platform. In addition to existing DRAM-side compliance measurement requirements, the client sought to simultaneously assess DDR signal quality at the CPU side. Through dual-endpoint measurements, the goal was to evaluate whether the overall channel design maintained sufficient design margin from a system-level perspective—providing a solid foundation for subsequent parameter tuning and risk assessment.

Customer Requirements and Practical Challenges: From “Measurable” to “Understandable and Actionable”

Because the platform did not reserve DRAM-side test access points during its initial design phase, it was not possible to directly perform standard electrical measurements in accordance with JEDEC specifications during later validation stages. Despite possessing complete test equipment and in-house capabilities, the client was constrained by limited measurement interfaces, making it difficult to obtain representative data suitable for compliance judgment. This became the primary bottleneck in the validation process.

The client’s objective extended beyond determining whether a single endpoint passed specification testing. Instead, the goal was to comprehensively understand the actual signal quality of the DDR memory channel from a system perspective, including:

- Synchronous comparison of DDR4 electrical behavior between DRAM side and CPU side

- Identifying whether routing topology, packaging effects, or SoC PHY design factors were compressing timing margins

- Translating measurement observations into actionable system design feedback to support parameter tuning strategies such as read/write leveling and ODT optimization

- In practice, CPU-side measurements are limited by insufficient probe contact space and difficulties in waveform acquisition.

- The measurement results are not easily directly correlated with JEDEC specifications, putting considerable pressure on the internal team in terms of verification strategy planning and data interpretation.

Leveraging a consultative validation methodology, Allion’s engineering team assisted the client in integrating DRAM-side and CPU-side measurement results, transforming raw data into actionable insights that could be fed back into system design decisions.

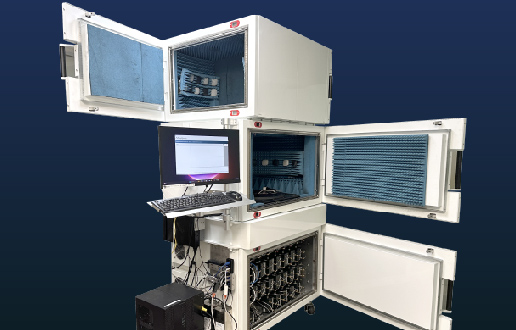

Solution: A Specification-Driven × System-Level Integrated Validation Strategy

To address these challenges, Allion introduced a validation framework combining specification-oriented analysis with system-level interpretation, establishing a structured and implementable validation architecture.

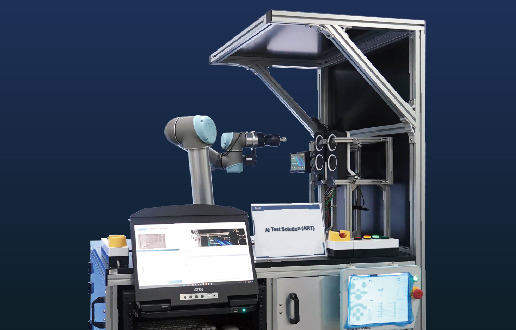

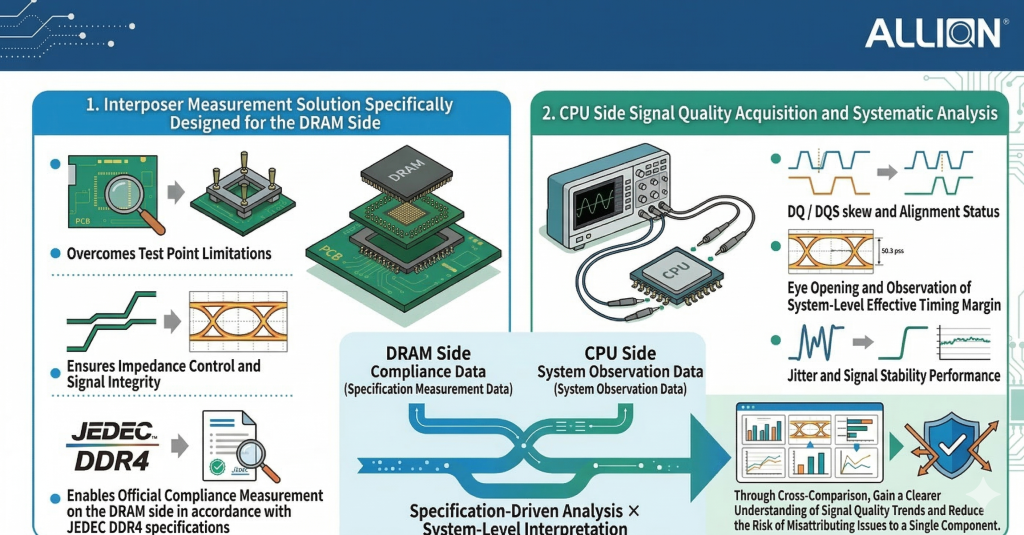

1. Custom Interposer Measurement Solution for DRAM Side

Drawing on extensive experience in high-speed fixture design and memory validation, Allion developed a custom DRAM measurement interposer (interposer/spacer board) that:

- Compensated for the lack of reserved test access points

- Maintained impedance control and signal integrity

- Enabled formal JEDEC DDR4-compliant electrical measurements at the DRAM side

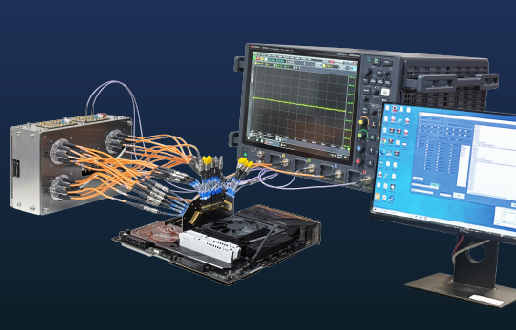

2. CPU-Side Signal Quality Capture and Systematic Analysis

While conducting DRAM-side compliance measurements, Allion simultaneously captured corresponding DQ/DQS waveforms at the CPU side using high-bandwidth oscilloscopes and low-loading differential probes. Key analysis items included:

- DQ/DQS skew and alignment

- Eye opening and effective system-level timing margin

- Jitter and overall signal stability

CPU-side measurements were not used for JEDEC compliance determination, but rather for internal comparative analysis and observation of channel behavior. Cross-correlation with DRAM-side compliance results enabled clearer insight into signal quality evolution along the channel and reduced the risk of over-attributing system-level issues to a single component or process factor.

Allion’s Core Value: From Measurement Data to Design-Driven Decisions

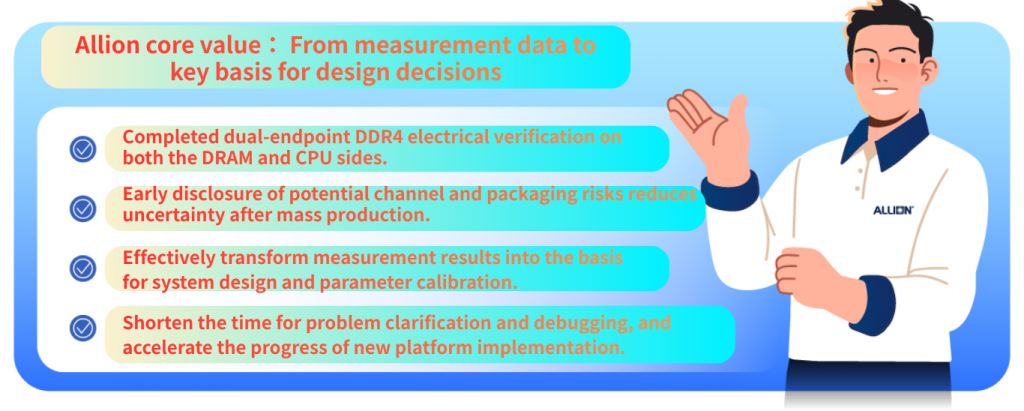

Through this integrated validation project, Allion helped the client:

DDR Validation Is Not Just About Compliance — It Is About Usability and Stability

In high-speed memory design, the real challenge is not merely passing specifications, but ensuring sufficient design margin and long-term system stability.

By combining standardized measurements, dedicated fixtures, and system-level analytical methodologies, Allion enables customers to move beyond single-point validation toward comprehensive channel understanding—transforming DDR electrical validation into a strategic tool that supports informed design decisions.

Looking ahead, Allion will continue leveraging its measurement expertise and consultative validation experience to serve as a trusted long-term technical partner in high-speed memory design for high-performance computing and server platforms.

Inquiry Form